Asynchronous Circuit and System Design Group

Asynchronous Open-Source DLX Processor (ASPIDA)

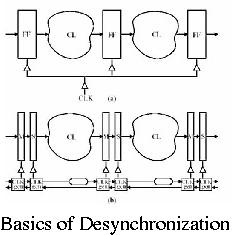

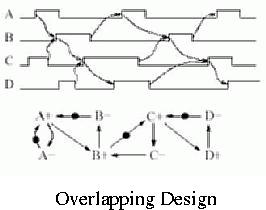

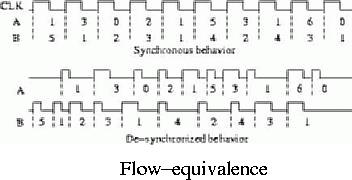

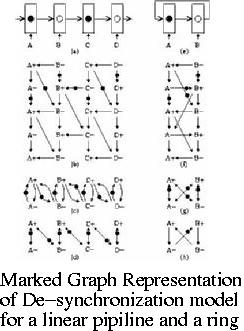

| Desynchronization: an easy approach to Asynchronous design |

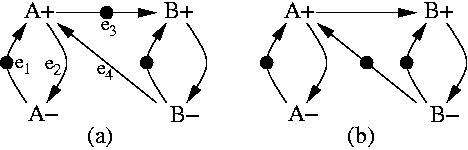

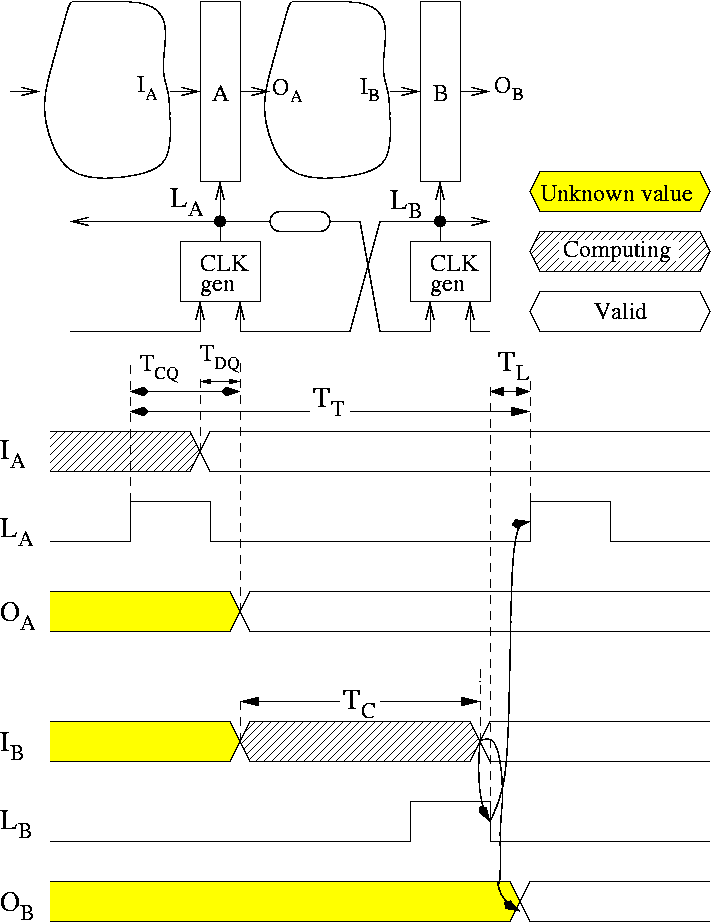

- J. Cortadella, A. Kondratyev, L. Lavagno and C. Sotiriou. A Concurrent Model for De-synchronization. In Handouts of the International Workshop on Logic Synthesis, pages 294-301, 2003. (pdf)

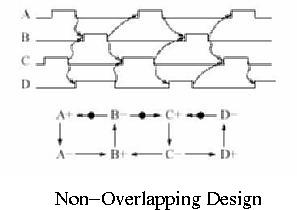

- I. Blunno, J. Cortadella, A. Kondratyev, K. Lwin and C. Sotiriou. Handshake Protocols for De-synchronization. In Proceedings of the 10th International Synposium on Asynchronous Circuits and Systems, April 2004. (pdf)

To read more about the principles of de-synchronization (parts of first paper) follow the clickable images below:

For more information on the implementation of the model click here...