| |

Asynchronous Circuit and System Design Group | ||

Asynchronous Open-Source DLX Processor (ASPIDA)

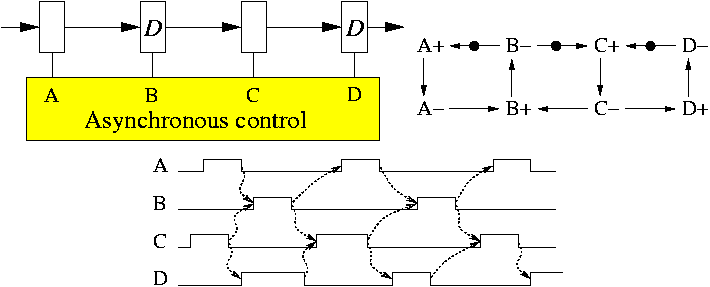

In the synchronous methodology, latched designs are normally clocked by two-phase non-overlapping clocks. The first model is a direct implementation of this scheme. A timing diagram and the corresponding marked graph for a simple pipeline is depicted in Fig. 1. The latches are transparent when the control signal is high. Initially, only half of the latches contain data (D). Data items flow in such a way that a latch never captures a new item before the successor latch has captured the previous one.

Since the pulses for adjacent latches are non-overlapping, data

overwriting can never occur. However, contrary to common belief,

the need for a non-overlapping scheme to avoid races could be relaxed.

|

|||