| |

Asynchronous Circuit and System Design Group | ||

Asynchronous Open-Source DLX Processor (ASPIDA)

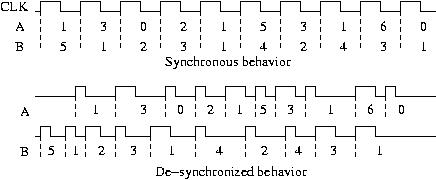

The de-synchronization model previously presented enables data to flow across an asynchronous circuit. But is this data flow equivalent to the behavior of the synchronous circuit? We now present the notion of flow-equivalence [5], which is related to that of synchronous behavior in [9], in terms of the projection of traces onto the latches of the circuit. Definition 3.1 (Flow equivalence) Two circuits are flow-equivalent if (1) they have the same set of latches and (2) for each latch A, the projections of the traces onto A is the same in both circuits.Intuitively, two circuits are flow-equivalent if their behavior cannot be distinguished by observing the sequence of values stored at each latch. This observation is done individually for each latch and, thus, the relative order at which values are stored in different latches can change.  Figure 1: Flow-Equivalence |

|||