| |

Asynchronous Circuit and System Design Group | ||

Asynchronous Open-Source DLX Processor (ASPIDA)

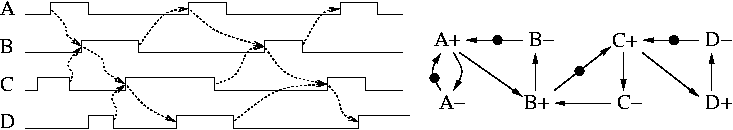

Figure 1 shows another model that allows clock pulses of adjacent latches to overlap. This model is based on the observation that a data item can ripple through more than one latch, as long as the previous values stored in those rippling latches have already been captured by the successor latches. As an example, event B+ can fire as soon as data is available in A (arc A+ to B+) and the previous data in B has been captured by C (arc C- to B+). The formal model for this de-synchronization is depicted in the marked graph of Fig 1. The arc A- to A+ is included to model the alternation of A+ and A- at one end of the pipeline. This arc is redundant for the other events. It is easy to understand that the Non-Overlapping model can be obtained by reducing the concurrency of the model in Fig. 1. |

|||