Asynchronous Circuit and System Design Group

Asynchronous Open-Source DLX Processor (ASPIDA)

| Demo System Implementation |

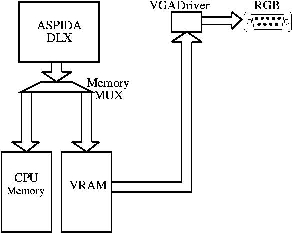

In the image above you can see a basic

block diagram of the Demo System. Clicking on it will show a larger

view of the block diagram.

To learn more about the memory interface and the memories click here...

To learn more about the VGA driver click here...