| |

Asynchronous Circuit and System Design Group | ||

Asynchronous Open-Source DLX Processor (ASPIDA)

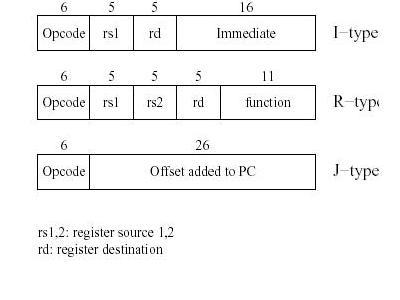

The ASPIDA DLX supports the three operation types of the DLX ISA:

|

|||

| ICS > CARV > ASYNC > Activities > ASPIDA | |||||||||

|

|||||||||

| About CARV | People | Packet Switch Architecture | Advanced Computing Systems | Asynchronous Circuits and Systems | Scalable Systems and Networks | News | Publications | Contact Info Site Map | Search | Help | Greek | English |

|||||||||

Last revision date: 04 Oct, 2005 by webmaster@ics.forth.gr |

|||||||||

Last Content revision date: 04 Oct, 2005 by Asynchronous Circuits and Systems Group. URL: http://www.ics.forth.gr/carv/async/news.html |

|||||||||